# **ADVANCE PROGRAM**

# 2023 IEEE INTERNATIONAL SOLID-STATE CIRCUITS CONFERENCE

FEBRUARY 19, 20, 21, 22, 23

# **CONFERENCE THEME:**

BUILDING ON 70 YEARS OF INNOVATION IN SOLID-STATE CIRCUIT DESIGN EVENT

SAN FRANCISCO Marriott Marquis Hotel

DRAFT 2-8-2023

4 FORUMS: A FORUMS: DVANCING TECHNOLOGES FOR XR: EXTREME DATA CONVERTERS HETEROGENEOUS MULT-CORE ARCHITECTURES FOR AL; WEARABLE & IMPLANTABLE DEVICES

ode Passive Mixers & N-Path IN

UTOMOTIVE SYSTEM |

SHORT-COURSE: Quartum Computing & the Application of Crydeletronics

HYSIGAL-LAYER SECURITY FOR LATENCY. ART OF MM-WAVE: DIGITAL EQUALIZATION & TIMING REGOVERY: EXTENDING PROGESSOR CORES FOR 1

RF AND POWER: |

<u>Concepts to Future Trends, Solid-Si</u>

UNDAMENTALS OF

<u>3 FORUMS: Transceivers for Exascale;</u> Future of Automotive Teehnology; Wireless Power Amplification

5-DAY Program

# IEEE SOLID-STATE CIRCUITS SOCIETY

# **ISSCC VISION STATEMENT**

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and application to maintain technical currency, and to network with leading experts.

# **CONFERENCE TECHNICAL HIGHLIGHTS**

On Sunday, February 19th, the day before the official opening of the Conference, ISSCC 2023 offers:

- A choice of 12 Tutorials, or

- A choice of 1 of 3 all-day Advanced-Circuit-Design Forums:

"Transceivers for Exascale: Towards Tbps/mm and sub-pJ/bit"

"The Power Behind Electrical Vehicles – Accelerating the Future of Automotive Technology "Efficient Wireless Power Amplification and Linearization"

The 90-minute tutorials offer background information and a review of the basics in specific circuit- and system-design topics. In the all-day Advanced-Circuit-Design Forums, leading experts present state-of-theart design strategies in a workshop-like format. The Forums are targeted at designers experienced in the technical field.

On Sunday, February 19th, there are two events: "Mentoring Session/Networking Bingo" will be offered starting at 3:00 pm. In addition, the Student-Research Preview, featuring ninety-second introductory presentations followed by a poster session from selected graduate-student researchers from around the world will begin at 8:00 pm. The SRP will start with an inspirational lecture by Professor Mark Horowitz (Stanford University).

On Monday, February 20th, ISSCC 2023 at 8:30 am offers four plenary papers on the theme: "Building on 70 Years of Innovation in Solid-State Circuit Design". On Monday at 1:30 pm, there are five parallel technical sessions, followed by a Social Hour at 5:15 pm open to all ISSCC attendees. The Social Hour, held in conjunction with Book Displays and Author Interviews, will also include a Demonstration Session, featuring posters and live demonstrations of selected papers from industry and academia. Monday evening includes two events, entitled, "Integrated Circuits in an Interconnected World" and "The Path to Sustainable IC Ecosystems"

On Tuesday, February 21st, there are five parallel technical sessions, both morning and afternoon. Book Displays and Author Interviews, will also include a second Demonstration Session. Tuesday evening includes two events, entitled: *"The Smartest Designer in The Universe, Post-Pandemic!"* and *"What will be the Essential Skills for IC Designers in the Next Decade?"*

On Wednesday, February 22nd, there will be five parallel technical sessions, both morning and afternoon, followed by Author Interviews.

On Thursday, February 23rd, ISSCC offers a choice of five all-day events:

- A Short Course entitled:

"Principles of Quantum Computing and the Application of Cryoelectronics

to Qubit Control and Readout "

- Four Advanced-Circuit-Design Forums entitled: "Advancing Technologies for Extended Reality (XR) to Make the "Metaverse" Possible" "Extreme Data Converters and Their Peripherals " "The Future of Heterogeneous Multi-Core Architectures for AI and Other Specialized Processing" "Advanced Circuits and Technologies for Wearable and Implantable Devices"

This year, again, there is an option which allows an attendee to sample parts of all 5 Thursday offerings. Registration for educational events on Sunday and Thursday will be filled on a first-come first-served basis. Use of the ISSCC Web-Registration Site (http://www.isscc.org) is strongly encouraged. Registrants will be provided with immediate confirmation on registration for the Conference, Tutorials, Forums, and the Short Course.

Need Additional Information? Go to: www.isscc.org

# **Table of Contents**

| Tutor    | rials                                                                                                                                      | 5-10      |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          | FORUMS                                                                                                                                     |           |

| F1       | Transceivers for Exascale: Towards Tbps/mm and sub-pJ/bit                                                                                  | 11        |

| F2       | The Power Behind Electrical Vehicles –Accelerating the Future of Automotive Technology.                                                    | 12        |

| F3       | Efficient Wireless Power Amplification and Linearization                                                                                   | 13        |

| EE       | EVENING EVENIS<br>Mentoring Session/Networking Bingo Event                                                                                 | 14        |

| EE1      | Student Research Preview: Short Presentations with Poster Session                                                                          | 14        |

|          | PAPER SESSIONS                                                                                                                             |           |

| 1        | Plenary                                                                                                                                    | 15-16     |

| 2<br>3   | Digital Processors<br>Amplifiers and Oscillators                                                                                           |           |

| 3<br>4   | Frequency Synthesizers                                                                                                                     |           |

| 5        | Image Sensors                                                                                                                              |           |

| 6        | Advanced Wireline Links and Techniques                                                                                                     |           |

|          | Demonstration Session 1                                                                                                                    |           |

|          | EVENING EVENTS                                                                                                                             |           |

| EE2      | Integrated Circuits in an Interconnected World                                                                                             | 23        |

| EE3      | The Path to Sustainable IC Ecosystems                                                                                                      |           |

| LLU      | PAPER SESSIONS                                                                                                                             |           |

| 7        | SRAM Compute-In-Memory                                                                                                                     | 25        |

| 8        | GHz-to-Millimeter Wave Frequency Generation                                                                                                |           |

| 9        | Highlighted Chip Releases: Digital and Machine Learning Processors                                                                         |           |

| 10       | Pipelined and Noise-Shaping ADCs                                                                                                           |           |

| 11       | USB and Compute Power Delivery                                                                                                             | 28        |

| 12       | High Performance Optical Receivers                                                                                                         |           |

| 13       | Ideas for the Future                                                                                                                       |           |

| 14<br>15 | Digital Techniques for Clocking and Power Management                                                                                       |           |

| 16       | IOT & Security<br>Efficient Compute-In-Memory Based Processors for ML                                                                      |           |

| 17       | High-Speed Data Converters.                                                                                                                |           |

| 18       | mm-Wave & sub-THz for Wireless and Sensing                                                                                                 |           |

| 19       | 5G and Satcom: Receivers and Transmitters                                                                                                  |           |

| 20       | GaN Power Conversion                                                                                                                       | 34        |

| 21       | Emerging Sensing Systems and IOT                                                                                                           |           |

|          | Conference Timetable                                                                                                                       |           |

|          | Demonstration Session 2                                                                                                                    |           |

|          | EVENING EVENTS                                                                                                                             |           |

| EE4      | The Smartest Designer in The Universe, Post-Pandemic!                                                                                      |           |

| EE5      | What will be the Essential Skills for IC Designers in the Next Decade?                                                                     |           |

| 22       | PAPER SESSIONS Heterogenous ML Accelerators                                                                                                | 40        |

| 22       | Analog Sensor Interfaces                                                                                                                   | 40<br>//1 |

| 24       | THz Signal Generation                                                                                                                      | 42        |

| 25       | RF Transceiver Building Blocks                                                                                                             |           |

| 26       | Display and User Interaction Technologies                                                                                                  |           |

| 27       | Innovations from Outside the (ISSCC) Box                                                                                                   |           |

| 28       | High-Density Memories and High-Speed Interface                                                                                             |           |

| 29       | Digital Accelerators and Circuit Techniques                                                                                                |           |

| 30<br>31 | Power Management Techniques<br>Energy-Efficient Radios for UWB, BMI, and IoT Systems                                                       |           |

| 32       | Intelligent Biomedical Circuits and Systems                                                                                                |           |

| 33       | Non-Volatile Memory and Compute-In-Memory                                                                                                  |           |

| 34       | Crvo-CMOS for Quantum Computing                                                                                                            |           |

|          | SHORT COURSE                                                                                                                               |           |

| SC       | Principles of Quantum Computing and the Application                                                                                        | 51-52     |

|          | of Cryoelectronics to Qubit Control and Readout                                                                                            |           |

| - 4      | FORUMS                                                                                                                                     | = -       |

| F4       | Advancing Technologies for Extended Reality (XR) to Make the "Metaverse" Possible                                                          |           |

| F5<br>F6 | Extreme Data Converters and Their Peripherals<br>The Future of Heterogeneous Multi-Core Architectures for AI and Other Specialized Process |           |

| F0<br>F7 | Advanced Circuits and Technologies for Wearable and Implantable Devices                                                                    |           |

|          | Committees                                                                                                                                 |           |

|          | Conference Information                                                                                                                     |           |

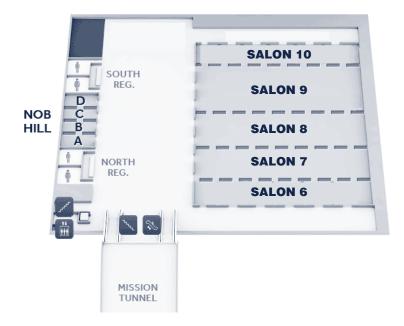

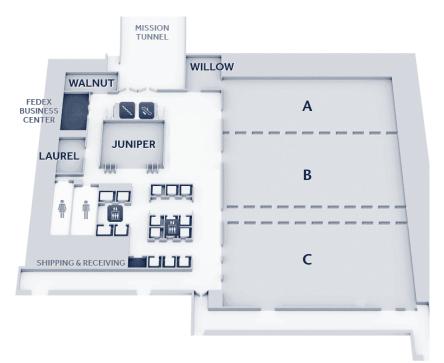

|          | Conference Space Layout                                                                                                                    |           |

# **ISSCC 2023 Circuit Insights**

#### **Organizer/Moderator:** Ali Sheikholeslami, University of Toronto, Toronto, Canada ISSCC Education Chair

ISSCC 2023 offers the second edition of its Circuit Insights on Saturday, Feb. 18, 2023, 7:30am -12:00pm PST. Like its initial debut in 2022, this event is targeting third-year undergraduate students and starting graduate students in the area of circuit design, but may be of interest to new circuit design engineers as well. The event will be held in person for a small audience of 50 students (by invitation only) at the ISSCC venue at the Marriott Hotel in San Francisco, and will be broadcast live via YouTube/Zoom worldwide. This event is free of charge but requires registration through isscc.org/insights.

The event consists of four 45-minute talks on fundamentals of Circuit Design, each to be followed by a 15-minute Q&A Session, with a 30-minute break after the second talk. The Q&A session will be interactive, entertaining questions from the in-person as well as the online attendees.

- -

| Agenda                 |                                                                                               |  |  |

|------------------------|-----------------------------------------------------------------------------------------------|--|--|

| <u>Time</u><br>7:00 AM | <b>Topic</b><br>Light Breakfast                                                               |  |  |

| 7:30 AM                | Opening Remarks<br>Ali Sheikholeslami, Circuit Insights Organizer/Moderator                   |  |  |

| 7:35 AM                | Welcoming Remarks<br>Eugenio Cantatore, ISSCC Conference Chair<br>John Long, SSCS President   |  |  |

| 7:40 AM                | The CMOS Latch<br>Asad Abidi, University of California, Los Angeles, CA                       |  |  |

| 8:25 AM                | Interactive Q & A                                                                             |  |  |

| 8:40 AM                | The Art of Linear Analysis for Analog Circuits<br>Jaeha Kim, Seoul National University, Korea |  |  |

| 9:25 AM                | Interactive Q & A                                                                             |  |  |

| 9:40 AM                | Break                                                                                         |  |  |

| 10:10 AM               | The Basics of Low Noise Amplifiers<br>Rabia Yazicigil Kirby, Boston University, MA            |  |  |

| 10:55 AM               | Interactive Q & A                                                                             |  |  |

| 11:10 AM               | The Basics of Analog-to-Digital Converters<br>Maurits Ortmanns, University of Ulm, Germany    |  |  |

| 11:55 AM               | Interactive Q & A                                                                             |  |  |

| 12:10 PM               | Attendees Feedback                                                                            |  |  |

| 12:20 PM               | Networking Lunch                                                                              |  |  |

| 1:30 PM                | Conclusion                                                                                    |  |  |

|                        |                                                                                               |  |  |

# TUTORIALS

# Sunday February 19th

There are a total of 12 tutorials this year on 12 different topics. Each tutorial, selected through a competitive process within each subcommittee of the ISSCC, presents the basic concepts and working principles of a single topic of broad interest. The tutorials are intended for non-experts, graduate students, and practicing engineers who wish to explore and understand a new topic. Tutorial registration bundles access to all 12 of the tutorials. Participants are asked to select between the option for only on-demand access to the tutorials (provided ahead of the conference) or the option to additionally attend a full-day live Q&A and networking session with the presenters during the conference, at no additional charge. The coordinators for the 2023 ISSCC Tutorials are (in the same order as the tutorials): Jens Anders (T1), Yan Lu (T2), Shahrzad Naraghi (T3), Chia-Hsiang Yang (T4), Eric J.-W. Fang (T5), Leonardo Gasparini (T6), Yih Wang (T7), Jeff Walling (T8), Noriyuki Miura (T9), Bodhisatwa Sadhu (T10), Byungsub Kim (T11), Jae-Sun Seo (T12).

#### Naveen Verma

ISSCC Tutorials Chair

The presentations of all 12 tutorials will be available online, on-demand, as of: Friday, Feb. 10, 2023, 5:00pm, PST

> Live Q&A in person for the tutorials: Sunday Feb. 19, 2023

# 10:00 AM - Live Q&A in person - February 19 T1: Fundamentals of Frequency References Danielle Griffith, Texas Instruments, Dallas, TX

Frequency references are a fundamental building block in a vast array of electronic systems. This tutorial will introduce several types of oscillators commonly used as frequency references, including crystal and MEMS oscillators as well as fully-integrated oscillators. Classical circuit architectures and recent advances will be shown. The tutorial will focus on how system-level requirements influence the circuit-level architecture, the required frequency accuracy, power consumption, and other design targets. Design tradeoffs will be described for each oscillator type. At the end of this tutorial, attendees will have a solid understanding of frequency reference specifications, common oscillator architectures, tradeoffs, and recent innovations in the field.

**Danielle Griffith** received the B.S.E.E. and M.Eng. degrees from the Massachusetts Institute of Technology. She is currently a Fellow at Texas Instruments in Dallas, Texas. Her areas of expertise are circuits and architectures for efficient wireless systems, low power oscillators, and MEMS circuitry. She has published a book chapter and >50 papers, and holds 22 issued US patents. Danielle has presented at numerous conference tutorial and workshop sessions. She has been a TPC member for the RFIC, ISSCC, and VLSI conferences. She is a senior member of the IEEE, an associate editor of the IEEE JSSC, and a Distinguished Lecturer of the SSCS.

# 10:20 AM - Live Q&A in person - February 19 T2: Bridging RF and Power: An Introduction to Envelope Tracking Systems and Building Blocks

# Ji-Seon Paek, Pusan National University, Pusan, Korea

Envelope tracking (ET) is a well-established power-management technique to improve the power efficiency of RF power amplifiers. This tutorial covers the principles of envelope-tracking operation, and the design of building blocks under ET-system link budget considerations. It develops the understanding of standard-specific system specifications, required by 3GPP and IEEE standards, to enable optimal design of each building block. Based on the understanding, various supply-modulator (SM) structures and power-management circuit techniques will be reviewed, which can efficiently power RF power amplifiers while meeting the requirements of wireless communication standards.

Jiseon Paek received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2004, 2006, and 2011, respectively. Since 2011, he has been with Samsung Electronics, where he leads various projects developing wireless RF transceivers, envelope tracking (ET) ICs, and fully integrated power ICs for mobile handset applications. Since 2022, he has been an Associate Professor in the Department of Electronics Engineering at Pusan National University (PNU), Korea. He is now serving on the power management sub-committee of ISSCC.

# 10:40 AM - Live Q&A in person - February 19

# T3: Fundamentals of Data Converters

Yun Chiu, University of Texas at Dallas, Richardson, TX

A refreshing review of fundamental data-conversion principles and circuit techniques, ranging from the concepts of sampling and quantization, to flash, pipeline and SAR architectures, to common circuit building blocks, to time- and frequency-domain measurement techniques of converters, will be presented in this tutorial. An emphasis will be placed on performance robustness, digital correctability, and calibration in advanced process nodes. The tutorial will wrap up with a historic remark on and a future perspective of the ADC Figure-of-Merits.

Yun Chiu is an Erik Jonsson Distinguished Professor of the ECE Department of the University of Texas at Dallas, where he directs the Analog and Mixed-Signal Lab at the Texas Analog Center of Excellence. His industry experience includes working as a Senior Staff Member in a Silicon Valley startup in the late 90s and co-founding Formula Microelectronics in 2015 during his sabbatical leave. He has served on the technical program committees of VLSI-C, CICC, and A-SSCC. He is now serving on the data converter subcommittee of ISSCC. He received his Ph.D. from UC Berkeley.

# 11:00 AM - Live Q&A in person - February 19 T4: Automotive System Design

Sugako Otani, Renesas Electronics, Tokyo, Japan

The automotive industry is in the midst of a significant transformation. "CASE: Connected, Autonomous, Shared & Service, Electric" has been advocated as a trend. Along with this trend, automotive E/E (Electrical/Electronic) architecture has rapidly progressed toward ECU (Electronic Control Unit ) integration and centralization in the autonomous driving era. The tutorial introduces automotive system design and key technologies of LSI devices, including processors for advanced vehicle control and cognitive/judgment processing. Multiple safety mechanisms for automotive functional safety are also covered.

**Sugako Otani** is a system and processor architect at Renesas Electronics Corporation. Her current research focuses on application-specific architectures, ranging from IoT devices to automotive. She joined Mitsubishi Electric Corporation, Japan, in 1995 after receiving an M.S. in physics from Waseda University, Tokyo. She received a Ph.D. in Electrical Engineering and Computer Science from Kanazawa University in 2015. From 2005 to 2006, she was a Visiting Scholar at Stanford University. She is a committee member of ISSCC, VLSI Symposium, ESSCIRC, and Cool Chips. Since 2019, she has been a Visiting Associate Professor at Nagoya University, Japan.

# 11:20 AM - Live Q&A in person - February 19 T5: All-Digital PLLs: From Fundamental Concepts to Future Trends Akihide Sai. Toshiba. Kawasaki. Japan

Frequency synthesis has become ubiquitous in chip designs for clocking, RF, and data sampling. Traditional analog PLLs have moved to digital implementations, for area, power, and technology portability. This tutorial describes the evolution of all-digital PLLs, from the basic digitization of oscillator control at integer ratios, to low-noise flexible fractional-N frequency synthesis with digital-to-time converters (DTCs). The evolution of two noise-critical blocks is described: time-to-digital converters (TDCs) and fractional dividers. This includes voltage-based TDCs, such as time amplifiers and successive-approximation-register (SAR) architectures, and various DTCs for fractional-divider noise reduction. It concludes with architectures at the limits of noise and size, namely bang-bang TDCs, and looks at future digital PLL trends. The presentation emphasizes key considerations for digital systems, including fast dynamic frequency scaling (DFS), fine resolution, and noise mitigation.

# TUTORIALS

# Sunday February 19th

**Akihide Sai** received the B.E. and M.E. degrees from Waseda University, Tokyo, Japan, in 2002 and 2004, respectively. In 2004, he joined the Corporate Research and Development Center, Toshiba Corporation, Kawasaki, Japan. From 2004 to 2015, he has been engaged in the research and development of low-power transceivers and digital/analog phase-locked loops (PLLs). Since 2016, he has been a senior research scientist and a team leader of mixed-signal circuits for automobile LiDAR SoCs. He contributed to high-performance mixed-signal circuit and LiDAR system projects and co-authored more than 20 technical papers and patents.

# 11:40 AM - Live Q&A in person - February 19 T6: Solid-State CMOS LiDAR Sensors

# Seong-Jin Kim, Ulsan National Institute of Science and Technology, Ulsan, Korea

This tutorial will present the technologies behind single-photon avalanche-diode (SPAD)-based solid-state CMOS LiDAR sensors that have emerged to realize level-5 automotive vehicles and the metaverse AR/VR in mobile devices. It will begin with the fundamentals of direct and indirect time-of-flight (ToF) techniques, followed by structures and operating principles of three key building blocks: SPAD devices, time-to-digital converters (TDCs), and signal-processing units for histogram derivation. The tutorial will finally introduce the recent development of on-chip histogramming TDCs with some state-of-the-art examples.

**Seong-Jin Kim** received a Ph.D. degree from KAIST, Daejeon, South Korea, in 2008 and joined the Samsung Advanced Institute of Technology to develop 3D imagers. From 2012 to 2015, he was with the Institute of Microelectronics, A\*STAR, Singapore, where he was involved in designing various sensing systems. He is currently an associate professor at Ulsan National Institute of Science and Technology, Ulsan, South Korea, and a co-founder of SolidVUE, a LiDAR startup company in South Korea. His current research interests include high-performance imaging devices, LiDAR systems, and biomedical interface circuits and systems.

# 1:00 PM - Live Q&A in person - February 19 T7: Fundamentals of Ultra-Low Voltage Embedded Memory Design

Eric Karl, Intel, Portland, OR

To meet the energy efficiency demands of future applications, system-on-chip (SoC) designs continue to march towards ultra-low-voltage operation. This tutorial will address the fundamental challenges for embedded memory operation at low voltages in advanced process technologies, and cover single and multi-port SRAM, logic flip-flop, logic latch arrays, and eFuse technologies, prevalent in embedded design use. Memory assist circuits, repair, error correction, multi-VCC array design, clocking and min-delay design strategies relevant to enabling ultra-low and near-threshold system operation will be explored. System designers will walk away with a stronger understanding of how to better navigate embedded memory usage in ultra-low-voltage designs.

**Eric Karl** is an Intel Fellow, Director of Advanced Design and Director of Embedded Memory Technology and Circuits. Karl leads the Advanced Design group in Intel's Technology Development organization, where he is responsible for standard-cell library architecture, memory and analog circuit technologies employed by all designers on Intel technology. Karl leads teams at Intel responsible for design technology cooptimization and develops a wide-range of circuits for early development test vehicles to enable technology development. Karl played a lead role in Intel's embedded memory technology development and the transition to FinFET technology in 2012. Karl holds doctoral, master's and bachelor's degrees in electrical engineering from the University of Michigan, Ann Arbor. He has published over 30 peer-reviewed technical papers, holds numerous patents and is currently serving on the memory subcommittee of the International Solid-State Circuits Conference (ISSCC).

# 1:20 PM - Live Q&A in person - February 19 T8: Role of Current-Mode Passive Mixers and N-Path Filters in RF Receivers

# Masoud Babaie, Delft University of Technology, Delft, The Netherlands

Modern multimode sub-6GHz receivers heavily employ current-mode passive mixers and N-path filters to simultaneously satisfy the noise requirements and deal with large in-band and out-of-band interferences. After a brief description of a typical receiver structure and its performance matrix, the operation of currentmode receivers and N-path filters will be explained in detail. In particular, this tutorial will focus on the impedance transformation property and reciprocal mixing of those structures. The tutorial will then cover architectures and applications exploiting N-path filters, such as high-order programmable bandpass filters, magnetic-free circulators, mixer-first, and low-noise trans-impedance amplifier (LNTA)-based receivers.

**Masoud Babaie** is a associate professor at the Delft University of Technology, The Netherlands. His research interests include RF/millimeter-wave integrated circuits and systems for wireless communications. He has authored or co-authored one book, three book chapters, 11 patents, and over 80 technical articles. Dr. Babaie serves on the technical program committee of the IEEE ISSCC and is the co-chair for the emerging computing devices and circuits subcommittee of IEEE ESSCIRC. He was a co-recipient of the 2019 IEEE ISSCC demonstration-session certificate of recognition and the 2020 IEEE ISSCC Jan Van Vessem Award for outstanding European paper. He also received the Veni grant from the Netherlands Organization for Scientific Research (NWO) in 2019.

# 1:40 PM - Live Q&A in person - February 19 T9: Physical-Layer Security for Latency- and Energy-Constrained Integrated Systems

# Rabia Tugce Yazicigil, Boston University, Boston, MA

The boom of connected IoT nodes and ubiquity of wireless communications are projected to increase wireless data traffic by several orders of magnitude in the near future. While these future scalable networks support increasing numbers of wireless devices utilizing the EM spectrum, ensuring the security of wireless communications and sensing is also a critical requirement under tight resource constraints. The physical layer has increasingly become the target of attacks by exploiting hardware weaknesses, e.g., side-channel attacks/fault injection/direct probing, and signal properties, e.g., time, frequency, and modulation characteristics. This tutorial introduces common security vulnerabilities within wireless systems such as jamming, eavesdropping, counterfeiting and spoofing, followed by physical-layer countermeasures, while assessing the trade-offs between performance and security. It examines recent research directions, e.g., secure spatio-temporal modulated arrays, temporal swapping of decomposed constellations, RF fingerprinting, bit-level frequency hopping, and integrated physical-attack-detection (anomaly-detection) sensors, and reaction circuits, and finally discusses research opportunities looking forward.

**Rabia Yazicigil** is an Assistant Professor in the ECE Department at Boston University and a Visiting Scholar at MIT. She was a Postdoctoral Associate at MIT and received her PhD degree from Columbia University in 2016. Her research interests lie at the interface of integrated circuits, signal processing, security, bio-sensing, and wireless communications to innovate system-level solutions for future energy-constrained applications. She has received numerous awards, including the "Electrical Engineering Collaborative Research Award" for her PhD research (2016), second place at the Bell Labs Future X Days Student Research Competition (2015), and 2014 Millman Teaching Assistant Award of Columbia University. She served as the Vice Chair of the Rising Stars 2020 workshop at the ISSCC. She is a member of the ISSCC and ESSCIRC TPCs and 2015 MIT EECS Rising Stars cohort.

# **TUTORIALS**

# Sunday February 19th

# 2:00 PM - Live Q&A in person - February 19 T10: The Art of mm-Wave Design and Layout Shahriar Shahramian, Nokia – Bell Labs, New Providence, NJ

We live in the golden age of mm-wave ASIC design! With the rise of 5G networks & 6G research, a massive push for commercialization of mm-wave integrated circuits is underway. This tutorial explores the hidden impairments that are often overlooked or difficult to locate in mm-wave layouts and interconnects. Using real-life fabricated circuit blocks operating up to and beyond D-band (170GHz), as well as optical circuits operating beyond 100Gb/s, the tutorial will explore layout challenges and impairments that can adversely affect the circuit performance. After modeling these elements, simulations demonstrate the impact of the parasitics on bandwidth, center frequency, stability, and noise figure. Using simple and quick modeling techniques, the designers can incorporate effects of various layout parasitics. Furthermore, mm-wave techniques at the chip level are explored from ground planes to flip-chip bumps. Finally, going beyond the boundaries of integrated circuits, co-design techniques will be explored to carry mm-wave signals into packages, printed circuit boards, and antennas.

Shahriar Shahramian received the Ph.D. degree from University of Toronto in 2010 where he focused on the design of mm-wave data converters and transceivers. Dr. Shahramian has been with Bell Laboratories – Nokia since 2009 and is currently the Director of the Communication & Sensing ASICs Research Group. His research focus includes the design of mm-wave wireless and wireline integrated circuits and systems. Dr. Shahramian is a Bell Labs Fellow and leads the design and architecture of several state-of-the-art ASICs for optical coherent and wireless backhaul products. Shahriar serves as the chair of the mm-Wave & THz subcommittee of IEEE BICTS, as well as chair of mm-Wave SoCs at IEEE RFIC, and is a member of the technical program committee of IEEE ISSCC. He has also served as the Guest Editor of the IEEE Journal of Solid-State Circuits (JSSC). Dr. Shahramian has been the recipient of an Ontario Graduate Scholarship and a University of Toronto Fellowship. He also received the best paper awards at the CSICS Symposium in 2005 and 2015, the RFIC Symposium in 2020. He holds an Adjunct Associate Professor position at Columbia University, has received several teaching awards and is the founder and host of The Signal Path educational video series. Dr. Shahramian has presented short courses and workshops at the IEEE CSICS, BCTM, BCICTS, RFIC/IMS and ISSCC conferences.

# 2:20 PM - Live Q&A in person - February 19 T11: Digital Equalization and Timing Recovery Techniques for ADC-DSP Based High-Speed Links

## Masum Hossain, University of Alberta, Edmonton, Canada

As we move beyond 200Gb/s, equalization and timing-recovery techniques have evolved drastically, with ISI and latency playing a significant role in DSP-based receivers, especially with multi-level signaling. This tutorial aims at bridging the gap between well-understood analog/mixed-signal solutions and today's DSP-based solutions. Starting from traditional analog architectures, the tutorial will walk through the evolution toward today's DSP-based equalization and timing recovery. The tutorial will include digital equalization, timing recovery, their interaction, and interdependency. MLSD, a recent trend in DSP-based equalization will also be covered.

**Masum Hossain** received the B.Sc. degree from the Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, in 2002, the M.Sc. degree from Queen's University, Kingston, ON, Canada, in 2005, and the Ph.D. degree from the University of Toronto, Toronto, ON, in 2010. From 2008 to 2010, he was with the Analog and Mixed-Signal Division, Gennum Corporation, Burlington, ON. From 2010 to 2012 he was with Rambus Laboratory, Sunnyvale, CA, USA, as a Senior Member of Technical Staff. In 2013, he joined the Department of Electrical and Computer Engineering, University of Alberta, Edmonton, AB, Canada. Dr. Hossain was a recipient of the Best Student Paper Award at the 2008 IEEE Custom Integrated Circuits Conference and the Analog Device's Outstanding Student Designer Award in 2010. In 2021 he received EPS society nominated best paper award in IEEE Transaction in Components, Packaging and Manufacturing.

# 2:40 PM - Live Q&A in person - February 19 T12: Extending Processor Cores for Machine Learning Luca Benini, ETH Zürich and UNIBO, Zurich, Switzerland

Many low-cost, ultra-low-power applications require flexibility and cannot afford the large silicon budget of a specialized machine-learning/artificial-intelligence (ML/AI) accelerator. The tutorial will review the key ideas and approaches to extend the instruction-set architecture (ISA) and microarchitecture, as well as the digital design of processor cores to achieve high efficiency for ML. ISA extension examples (e.g. ARM's Helium and RISC-V extensions) will be analyzed, along with implementation challenges and solutions, drawing insights from various silicon-proven RISC-V cores.

**Luca Benini** holds the Chair of Digital Circuits and Systems at ETH Zürich and is a Full Professor at Università di Bologna. He served as chief architect in STmicroelectronics, France, from 2009-2012. He received a PhD from Stanford University. His research interests are in energy-efficient parallel computing systems, smart sensing micro-systems and machine learning hardware. He is a Fellow of the IEEE, Fellow of the ACM, and a member of the Academia Europaea. He is the recipient of the 2016 IEEE CAS Mac Van Valkenburg award, the 2019 IEEE TCAD Donald O. Pederson Best Paper Award and the ACM/IEEE A. Richard Newton Award 2020.

# Transceivers for Exascale: Towards Tbps/mm and sub-pJ/bit

| Organizers: | Tamer Ali, Mediatek, Irvine, CA<br>Didem Turker Melek, Cadence Design Systems, San Jose, CA                |

|-------------|------------------------------------------------------------------------------------------------------------|

| Committee:  | Munehiko Nagatani, NTT, Atsugi, Japan<br>Thomas Toifl, Cisco Systems, Wallisellen, Switzerland             |

| Champions:  | Franz Dielacher, Villach, Austria<br>Bill Redman-White, HiLight Semiconductor, Southampton, United Kingdom |

Connectivity is a key enabler of exascale computing systems. The forum covers electrical and optical transceivers used throughout these systems, from short die-to-die interconnect to long-distance network interfaces. In addition to state-of-the-art standard and proprietary interfaces, the forum also covers emerging and future works that will significantly increase interface bandwidth and power efficiency, and the design challenges of building high-performance connectivity chips.

## Agenda

| <u>Time</u><br>8:00 AM | Topic<br>Breakfast                                                                                                                            |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 8:15 AM                | Introduction<br>Tamer Ali, Mediatek, Irvine, CA                                                                                               |

| 8:25 AM                | High-Density, Energy-Efficient Interconnect Technologies Inside<br>Supercomputers<br>Yuichiro Ajima, Fujitsu, Kawasaki, Japan                 |

| 9:10 AM                | Bandwidth-Density- and Energy-Optimized Die-to-Die Interfaces<br>Elad Alon, Blue Cheetah, Sunnyvale, CA                                       |

| 9:55 AM                | Break                                                                                                                                         |

| 10:10 AM               | Advanced Packaging and 3D-IC Interconnections<br>Shenggao Li, TSMC, San Jose, CA                                                              |

| 10:55 AM               | PCle Rising: The Journey to 64Gb/s and 128Gb/s<br>Marc Loinaz, Cadence, San Jose, CA                                                          |

| 11:40 AM               | Circuit Designs for 200+Gb/s Transceivers<br>Jihwan Kim, Intel, Hillsboro, OR                                                                 |

| 12:25 PM               | Lunch                                                                                                                                         |

| 1:40 PM                | Electronics and Photonics for Beyond 200G Capable Transceivers<br>Peter Ossieur, imec, Ghent, Belgium                                         |

| 2:25 PM                | Direct-drive Optical I/O using Monolithic Silicon Photonics Integration<br>Christoph Schulien, Ranovus, Nuremberg, Germany                    |

| 3:10 PM                | Break                                                                                                                                         |

| 3:25 PM                | Advancements in High-Speed Electrical Terahertz Waveguide<br>Interconnects<br>Hyeon-Min Bae, KAIST/Point2-technology, Daejeon, Korea          |

| 4:10 PM                | Realizing Petabit/s IO and sub-pJ/bit System-Wide Communication<br>with Silicon Photonics<br>Keren Bergman, Columbia University, New York, NY |

| 4:55 PM                | Closing Remarks                                                                                                                               |

# The Power Behind Electrical Vehicles – Accelerating the Future of Automotive Technology

| Organizer: | Min Chen, Innoscience America, Santa Clara, CA                                                                                                                                  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Committee: | Kousuke Miyaji, Shinshu University, Nagano, Japan<br>Frank Praemassing, Infineon Technologies, Villach, Austria<br>Marco Berkhout, Goodix Technology, Nijmegen, The Netherlands |

| Champion:  | Bruce Rae, STMicroelectronics, Edinburgh, United Kingdom                                                                                                                        |

Vehicle electrification in EV/HEV is demanding unprecedented power electronic devices, circuits, and systems. This forum provides a comprehensive overview of the mega trend and design challenges on all levels, specifically related to battery protection and management systems, drivetrain topologies & systems, power semiconductor devices and modules, supplemental power electronics, automotive sensors, PMIC, and LED drivers.

#### Agenda

| <u>Time</u><br>8:00 AM | Topic<br>Breakfast                                                                                                                                        |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:15 AM                | Introduction<br>Min Chen, Innoscience America, Santa Clara, CA                                                                                            |

| 8:25 AM                | Mega Trends in Vehicle Electrification and Future EV Technology<br>Francesco Gennaro, STMicroelectronics, Catania, Italy                                  |

| 9:15 AM                | The Battery System is the Core of Future Mobility<br>Patrick Leteinturier, Infineon Technologies, Neubiberg, Germany                                      |

| 10:05 AM               | Break                                                                                                                                                     |

| 10:20 AM               | Trends and Research Cases of 800V Motor Drive Circuits for Battery<br>Electric Vehicle<br>Tomonori Kimura, MIRISE Technologies, Nisshin, Japan            |

| 11:10 AM               | The Opportunity from GaN and for GaN in Cars<br>Alex Lidow, EPC, El Segundo, CA                                                                           |

| 12:00 PM               | Lunch                                                                                                                                                     |

| 1:20 PM                | Power Electronics Components: MCU, Isolated Gate Driver,<br>Isolated Power Supply, and Sensors<br>Shunichi Kaeriyama, Renesas Electronics, Kodaira, Japan |

| 2:10 PM                | Long-Range High-Resolution LiDAR Technology<br>Katsuyuki Kimura, Toshiba, Kawasaki, Japan                                                                 |

| 3:00 PM                | Break                                                                                                                                                     |

| 3:15 PM                | Smart Power ASICs: System Definer and Not Just Components<br>Tamer Sinanoglu, Bosch, Reutlingen, Germany                                                  |

| 4:05 PM                | High-Efficiency LED Drivers for Automotive Applications<br>Hoi Lee, University of Texas at Dallas, Dallas, Texas                                          |

| 4:55 PM                | Closing Remarks                                                                                                                                           |

|                        |                                                                                                                                                           |

# Efficient Wireless Power Amplification and Linearization

| Organizers: | James Buckwalter, University of California, Santa Barbara, Santa Barbara, CA<br>Jeff Walling, Virginia Tech, Blacksburg, VA                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Committee:  | Hongtao Xu, Fudan University, Shanghai, China<br>Byung-Wook Min, Yonsei University, Seoul, Korea<br>Giuseppe Gramegna, imec, Leuven, Belgium<br>Wu-Hsin Chen, Qualcomm, San Diego, CA |

Champion: Andreia Cathelin, STMicroelectronics, Crolles Cedex, France

This forum reviews the state-of-the-art for power amplification and digital predistortion technologies from RF to mm-wave frequencies with applications to cellular, wifi, and satellite communications. Speakers are chosen to cover advances in CMOS/BiCMOS as well as GaAs/GaN process technologies that comprehensively connect underlying devices, circuits, and system architectures. The forum will also cover the emerging capabilities of digital signal processing for analog and digital PAs in RF bands and mm-wave arrays.

Agondo

| Agenda                 |                                                                                                                                            |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <u>Time</u><br>8:00 AM | <u>Topic</u><br>Breakfast                                                                                                                  |  |  |

| 8:15 AM                | Introduction<br>James Buckwalter, University of California, Santa Barbara,<br>Santa Barbara, CA                                            |  |  |

| 8:25 AM                | Emerging Device Technologies for RF/mm-Wave FEM<br>Nicholas Comfoltey, GlobalFoundries, San Diego, CA                                      |  |  |

| 9:15 AM                | Linear GaAs Technologies for Mobile Power Amplifiers<br>David Danzilio, <i>WIN Semiconductors, Taoyuan, Taiwan</i>                         |  |  |

| 10:05 AM               | Break                                                                                                                                      |  |  |

| 10:20 AM               | Sub-8GHz Base Station Power Amplifiers and Linearization<br>Rui Hou, Ericsson, Stockholm, Sweden                                           |  |  |

| 11:10 AM               | Advances in Highly Efficient All-Digital CMOS Transmitters for<br>Wide Bandwidth Wireless Application<br>Ofir Degani, Intel, Haifa, Israel |  |  |

| 12:15 PM               | Lunch                                                                                                                                      |  |  |

| 1:20 PM                | Single Transformer-Based Compact Doherty PA for 5G RFICs and<br>Base-Stations<br>Hyun-Chul Park, Samsung, Hwaseong, Korea                  |  |  |

| 2:10 PM                | Digital Predistortion (DPD) for High-Efficiency 5G Radio Units<br>Zohaib Mahmood, <i>Maxlinear, Waltham, MA</i>                            |  |  |

| 3:00 PM                | Break                                                                                                                                      |  |  |

| 3:15 PM                | Digital Pre-Distortion for Large-Scale mm-Wave Arrays<br>Harish Krishnaswamy, Sivers Semiconductors, Chatham, NJ                           |  |  |

| 4:05 PM                | Machine-Learning-Assisted Approaches for Wideband DPD<br>Anding Zhu, University College Dublin, Dublin, Ireland                            |  |  |

| 4:55 PM                | Closing Remarks                                                                                                                            |  |  |

|                        |                                                                                                                                            |  |  |

# Mentoring Session/Networking Bingo Event (Open to all Attendees) 3:00 - 5:00 PM

Women in Circuits (WiC) together with ISSCC will be holding a networking and mentoring session on Sunday afternoon. Distinguished panelists from the "Integrated Circuits in an Interconnected World" panel, WiC members, and other participants will play getting-to-know-you bingo to promote engagement between various members of the community. This will give participants the chance to network and mingle with people across a spectrum of seniority in the field in a casual setting. This event is open to all ISSCC attendees and the public.

#### EE1: Student Research Preview (SRP) 8:00 PM

The Student Research Preview (SRP) will highlight selected student research projects in progress. The SRP consists a number of ninety-second presentations followed by a Poster Session, by graduate students from around the world, which have been selected on the basis of a short submission concerning their on-going research. Selection is based on the technical quality and innovation of the work. This year, the SRP will be presented in three theme sections: 1) RF and Analog, 2) Energy-Efficient Circuits and Systems, and 3) Compute-in-Memory (CIM), Artificial Intelligence (AI) and Security.

The SRP will include an inspirational lecture by Professor Mark Horowitz (Stanford University). SRP begins at 8:00 pm on Sunday, February 19th. It is open to all ISSCC registrants.

# SRP Organizing Committee

| Co-Chair:           | Jerald Yoo, National University of Singapore, Singapore           |

|---------------------|-------------------------------------------------------------------|

| Co-Chair:           | Mondira (Mandy) Pant, Intel, MA                                   |

| Advisor:            | Anantha Chandrakasan, MIT, MA                                     |

| Advisor:            | Jan Van der Spiegel, University of Pennsylvania, Philadelphia, PA |

| Media/Publications: | Laura Fujino, University of Toronto, Toronto, Canada              |

| A/V:                | Trudy Stetzler, Halliburton, Houston, TX                          |

# COMMITTEE MEMBERS

| Utsav Banerjee, IISC, India                          | Noriyuki Miura, Osaka University, Japan               |

|------------------------------------------------------|-------------------------------------------------------|

| Hsin-Shu Chen, National Taiwan University, Taiwan    | Phillip Nadeau, Analog Devices, MA                    |

| Po-Hung Chen, National Chiao Tung University, Taiwan | Mondira Pant, Intel, MA                               |

| Zeynep Deniz, IBM, NY                                | Negar Reiskarimian, Massachusetts Institute           |

| Sijun Du, Delft University of Technology,            | of Technology, MA                                     |

| The Netherlands                                      | Atsushi Shirane, Tokyo Institute of Technology, Japan |

| Antoine Frappe, University of Lille, France          | Mahsa Shoaran, EPFL, Switzerland                      |

| Hao Gao, Eindhoven University of Technology,         | Yildiz Sinangil, Apple, CA                            |

| The Netherlands                                      | Mahmut Sinangil, Nvidia, CA                           |

| Preet Garcha, Texas Instruments, TX                  | Filip Tavernier, KU Leuven, Belgium                   |

| Minkyu Je, KAIST, Korea                              | Chia-Hsiang Yang, National Taiwan University, Taiwan  |

| Matthias Kuhl, University of Freiburg, Germany       | Lita Yang, Meta, CA                                   |

| Jaydeep Kulkarni, University of Texas at Austin, TX  | Rabia Tugce Yazicigil, Boston University, MA          |

| Jiamin Li, Southern University of Science            | Jerald Yoo, National University of Singapore,         |

| and Technology, China                                | Singapore                                             |

| Carolina Mora Lopez, imec, Belgium                   | Milin Zhang, Tsinghua University, China               |

14

# Plenary Session — Invited Papers

Chair:

*Eugenio Cantatore,* Eindhoven University of Technology, Eindhoven, The Netherlands ISSCC Conference Chair

Associate Chair: *Piet Wambacq, imec, Heverlee, Belgium* ISSCC International Technical Program Chair

# FORMAL OPENING OF THE CONFERENCE

8:30 AM

# 1.1 Innovation For the Next Decade of Compute Efficiency 8:45 AM

Lisa Su, Chair and Chief Executive Officer, AMD, Austin, TX

Although traditional scaling has slowed over the past decade, we have made tremendous progress as an industry with new approaches including chiplet-based architectures, domain-specific accelerators, and advanced packaging technologies which have enabled major milestones including the first exascale supercomputers. As we look into the future, we need to accelerate the pace of innovation to drive the next decade of advancement in high-performance computing. By far, the largest limiting factor to delivering continued compounded growth in computation power is energy efficiency. In this paper, we highlight a holistic strategy for accelerating innovation in energy efficiency required for next-generation high-performance computing ad ultimately achieving zettascale performance. These approaches will be built on continued innovation in process technologies, modular chiplet architectures, and advanced packaging. Fully meeting the challenge will require new dimensions of improvement through extending domain-specific architectures to accelerate core algorithms in combination with wide-scale deployment of AI across all aspects of the system from transistors to software.

## 1.2 Shape the World with Mixed-Signal Integrated Circuits - Past, Present, and Future

9:20 AM

Akira Matsuzawa, Professor Emeritus of Tokyo Institute of Technology and CEO of Tech Idea, Kawasaki, Japan

The past 50 years has been an era in which analog equipment has been replaced by digital counterparts. Audio, TV, video, camcorder, camera, recording, wired connection, and wireless communication have been subject to digitization. The digitization of these devices and systems was due to the technological shift from bipolar to CMOS, and to the development of logic and memory circuits supported by scaling laws. In addition, design innovation in mixed-signal integrated circuits such as ADCs and DACs has shown to be indispensable. This talk will look back on the digitization of equipment and the mixed-signal integrated circuit technology that contributed to it. Further, we will look forward to future applications and developments.

| ISSCC, SSCS, IEEE AWARD PRESENTATIONS | 9:55 AM  |

|---------------------------------------|----------|

| BREAK                                 | 10:20 AM |

# **SESSION 1**

#### 1.3 EU Chips Act Drives Pan-European Full-Stack Innovation Partnerships

10:40 AM

Jo De Boeck, Executive Vice President and Chief Strategy Officer, imec & KU Leuven, Leuven, Belgium

In every aspect of our life and society, semiconductors play a major role. The pandemic in conjunction with supply chain hiccups and geopolitical tensions made all regions realize that they need to revisit their presence in the semiconductor value chain. The European Commission projected the ambition of achieving a 20% share of the global semiconductor production by 2030.

Europe can leverage existing strengths such as, among others, the unique position of equipment companies and leadership positions in 300mm semiconductor technology R&D. The Chips-for-Europe initiative will invest in pilot lines and ecosystems for chip manufacturing, embracing leading-edge and first-of-a-kind technologies. The pilot lines will allow early exploration of the potential impact of new technology features in advanced chip and system architectures. This will trigger increased demand and accelerate industrial uptake of the novel technologies. This type of innovation loop is also essential for deep-tech start-ups building their unique value proposition. The full-stack, networked model of industry collaboration is at the core of the EU Chips Act ambition and will impact different application domains such as heterogeneous cloud and distributed computing, connectivity, automotive, and health.

It is crucial for all this innovation potential that we, as an industry, consider that semiconductor manufacturing is resource-intensive with respect to energy, water, chemicals, and raw materials. Design-technology co-optimization (DTCO) and System-Technology co-optimization (STCO) methodologies can develop a framework for early sustainability assessments of logic technologies. Finally, we urgently need to get the message across that climate, health, safety, and human connectedness all require complex digital backbones, if we want to stand a chance of attracting the right talent.

# 1.4 5G Drives Exponential Increase in Processing Needs Across all Industries

11:15 AM

11:50 AM

11:55 AM

Erik Ekudden, Senior Vice President & Chief Technology Officer, Ericsson, Kista, Sweden

Across essentially all industrial sectors, advanced semiconductor technology is the key enabler for innovations in customer offerings and internal efficiencies. The increase in the value of data and the related push for AI are examples of forces that increase the demand for compute power, which translates to more complex and powerful silicon. Moore's Law, supported by rapidly evolving semiconductor technology and ever more advanced building practices and assembly technologies, has met the need for decades.

But what is driving 5G today? If we look at the processing requirements, it is the digital front-end, physical layer processing, and beam forming. Back in 2010, LTE/4G was a 20MHz carrier with two receive and two transmit branches, and there was a transmission time interval of one millisecond. Fast forward to where we are today on 5G with massive MIMO, we typically have 100MHz carrier bandwidth. That is a factor of five increase. We have 64 transmitter and 64 receiver radios, which is an increase by a factor of 32, and the transmission time is down to 0.5 milliseconds. In other words, there is only half the time to do 160 times more processing. This is driving an exponential increase in processing needs across the telecom business today, and will continue to do so as we race towards 6G. This talk will address whether the semiconductor industry is ready to tackle these challenges.

#### PRESENTATION TO PLENARY SPEAKERS

#### CONCLUSION

# **Digital Processors**

Session Chair: Shidhartha Das, AMD, Cambridge, United Kingdom Session Co-Chair: Ji-Hoon Kim, Ewha Womans University, Seoul, Korea

1:30 PM

# 2.1 "Zen 4": The AMD 5nm 5.7GHz x86-64 Microprocessor Core

DS1 B. Munger<sup>1</sup>, K. Wilcox<sup>1</sup>, J. Sniderman<sup>1</sup>, C. Tung<sup>1</sup>, B. Johnson<sup>2</sup>, R. Schreiber<sup>3</sup>, C. Henrion<sup>2</sup>, K. Gillespie<sup>1</sup>, T. Burd<sup>4</sup>, H. Fair<sup>1</sup>, D. Johnson<sup>2</sup>, J. White<sup>1</sup>, S. McLelland<sup>1</sup>, S. Bakke<sup>1</sup>, J. Olson<sup>1</sup>, R. McCracken<sup>1</sup>, M. Pickett<sup>2</sup>, A. Horiuchi<sup>2</sup>, H. Nguyen<sup>1</sup>, T. H. Jackson<sup>2</sup> <sup>1</sup>AMD, Boxborough, MA; <sup>2</sup>AMD, Fort Collins, CO; <sup>3</sup>AMD, Austin, TX; <sup>4</sup>AMD, Santa Clara, CA

2:00 PM

# 2.2 A 5G Mobile Gaming-Centric SoC with High-Performance Thermal Management in 4nm FinFET

B-J. Huang, A. Tsai, L. Hsieh, K. Chang, C-J. Tsai, J-M. Chen, E-W. Fang, S-Y. Hsueh, J. Ciao, B. Chen, C. Chang, P. Kao, E. Wang, H. H. Chen, H. Mair, S-A. Hwang MediaTek, Hsinchu, Taiwan

2:30 PM

#### 2.3 Amorphica: 4-Replica 512 Fully Connected Spin 336MHz Metamorphic Annealer with Programmable Optimization Strategy and Compressed-Spin-Transfer Multi-Chip Extension

K. Kawamura<sup>\*1</sup>, J. Yu<sup>\*1</sup>, D. Okonogi<sup>1</sup>, S. Jimbo<sup>1</sup>, G. Inoue<sup>1</sup>, A. Hyodo<sup>1</sup>, Á. L. García-Arias<sup>1</sup>, K. Ando<sup>2</sup>, B. H. Fukushima-Kimura<sup>2</sup>, R. Yasudo<sup>3</sup>, T. V. Chu<sup>1</sup>, M. Motomura<sup>1</sup> <sup>1</sup>Tokyo Institute of Technology, Yokohama, Japan <sup>2</sup>Hokkaido University, Sapporo, Japan <sup>3</sup>Kyoto University, Kyoto, Japan \*Equally Credited Authors (ECAs)

Break 3:00 PM

3:15 PM

# 2.4 A Fully Integrated End-to-End Genome Analysis Accelerator for Next-Generation Sequencing

Y-L. Chen\*<sup>1</sup>, C-H. Yang\*<sup>1</sup>, Y-C. Wu\*<sup>1</sup>, C-H. Lee<sup>2</sup>, W-C. Chen<sup>3</sup>, L-Y. Lin<sup>3</sup>, N-S. Chang<sup>3</sup>, C-P. Lin<sup>3</sup>, C-S. Chen<sup>3</sup>, J-H. Hung<sup>2,4</sup>, C-H. Yang<sup>1,2</sup> <sup>1</sup>National Taiwan University, Taipei, Taiwan; <sup>2</sup>GeneASIC Technologies, Hsinchu, Taiwan <sup>3</sup>Taiwan Semiconductor Research Institute, Hsinchu, Taiwan <sup>4</sup>National Yang Ming Chiao Tung University, Hsinchu, Taiwan

\*Equally Credited Authors (ECAs)

## 3:45 PM

# 2.5 A 28nm 142mW Motion-Control SoC for Autonomous Mobile Robots

*I-T. Lin<sup>1</sup>, Z-S. Fu<sup>1</sup>, W-C. Chen<sup>2</sup>, L-Y. Lin<sup>2</sup>, N-S. Chang<sup>2</sup>, C-P. Lin<sup>2</sup>, C-S. Chen<sup>2</sup>, C-H. Yang<sup>1</sup>* <sup>1</sup>National Taiwan University, Taipei, Taiwan <sup>2</sup>Taiwan Semiconductor Research Institute. Hsinchu, Taiwan

4:15 PM

# 2.6 VISTA: A 704mW 4K-UHD CNN Processor for Video and Image Spatial/Temporal Interpolation Acceleration

*K-P. Lin, J-H. Liu, J-Y. Wu, H-C. Liao, C-T. Huang* National Tsing Hua University, Hsinchu, Taiwan

4:45 PM

## 2.7 MetaVRain: A 133mW Real-Time Hyper-Realistic 3D-NeRF Processor with 1D-2D Hybrid-Neural Engines for Metaverse on Mobile Devices

*D. Han, J. Ryu, S. Kim, S. Kim, H-J. Yoo* Korea Advanced Institute of Science and Technology, Daejeon, Korea

# Amplifiers and Oscillators

Session Chair: Jens Anders, University of Stuttgart, Stuttgart, Germany Session Co-Chair: Shon-Hang Wen, MediaTek, Hsinchu, Taiwan

1:30 PM

# 3.1 A 120.9dB DR, -111.2dB THD+N Digital-Input Capacitively-Coupled Chopper Class-D Audio Amplifier

*H. Zhang*<sup>1</sup>, *M. Berkhout*<sup>2</sup>, *K. A. A. Makinwa*<sup>1</sup>, *Q. Fan*<sup>1</sup> <sup>1</sup>Delft University of Technology, Delft, The Netherlands <sup>2</sup>Goodix Technology, Nijmegen, The Netherlands

2:00 PM

## 3.2 A Chopper-Stabilized Amplifier with a Relaxed Fill-In Technique and 22.6pA Input Current

*T. Rooijers<sup>1,2</sup>, J. H. Huijsing<sup>1</sup>, K. A. A. Makinwa<sup>1</sup>* <sup>1</sup>Delft University of Technology, Delft, The Netherlands; <sup>2</sup>now at Broadcom, Bunnik, The Netherlands

2:15 PM

# 3.3 Bandpass Filter and Oscillator ICs with THD < -140dBc at $10V_{ppd}$ for Testing High-Resolution ADCs

*S. Šarkar<sup>1,2</sup>, R. Agarwal<sup>1</sup>, N. Krishnapura<sup>2</sup>* <sup>1</sup>Texas Instruments, Bangalore, India; <sup>2</sup>Indian Institute of Technology Madras, Chennai, India

2:30 PM

## 3.4 A 0.01mm<sup>2</sup> 10MHz RC Frequency Reference with a 1-Point On-Chip-Trimmed Inaccuracy of ±0.28% from –45°C to 125°C in 0.18μm CMOS

X. An<sup>\*1,2</sup>, S. Pan<sup>\*1,3</sup>, H. Jiang<sup>2</sup>, K. A. A. Makinwa<sup>1</sup> <sup>1</sup>Delft University of Technology, Delft, The Netherlands <sup>2</sup>Silicon Integrated, Eindhoven, The Netherlands; <sup>3</sup>Tsinghua University, Beijing, China \*Equally Credited Authors (ECAs)

Break 3:00 PM

3:15 PM

## 3.5 A 1.4μW/MHz 100MHz RC Oscillator with ±1030ppm Inaccuracy from -40°C to 85°C After Accelerated Aging for 500 Hours at 125°C

K-S. Park, N. Pal, Y. Li, R. Xia, T. Wang, A. Abdelrahman, P. K. Hanumolu University of Illinois, Urbana, IL

3:45 PM

#### 3.6 A 12/13.56MHz Crystal Oscillator with Binary-Search-Assisted Two-Step Injection OSD Achieving 5.0nJ Startup Energy and 45.8µs Startup Time

*H. Li<sup>1</sup>, K-M. Lei<sup>1</sup>, P-I. Mak<sup>1</sup>, R. P. Martins<sup>1,2</sup>* <sup>1</sup>University of Macau, Macau, China; <sup>2</sup>Instituto Superior Tecnico/University of Lisboa, Lisbon, Portugal

4:15 PM

#### 3.7 A 16MHz XO with 17.5µs Startup Time Under 10⁴ppm-∆F Injection Using Automatic Phase-Error Correction Technique

Z. Cai<sup>1</sup>, X. Wang<sup>1</sup>, Z. Wang<sup>1</sup>, Y. Yin<sup>1</sup>, W. Zhang<sup>1</sup>, T. Xu<sup>2</sup>, Y. Guo<sup>1</sup> <sup>1</sup>Nanjing University of Posts and Telecommunications, Nanjing, China; <sup>2</sup>Hefei University, Hefei, China

4:30 PM

#### 3.8 A 0.954nW 32kHz Crystal Oscillator in 22nm CMOS with Gm-C-Based Current Injection Control

Y. Zhang<sup>1</sup>, Y. You<sup>1</sup>, W. Ren<sup>1</sup>, X. Xu<sup>1</sup>, L. Shen<sup>1</sup>, J. Ru<sup>1</sup>, R. Huang<sup>1</sup>, L. Ye<sup>1,2</sup> <sup>1</sup>Peking University, Beijing, China <sup>2</sup>Advanced Institute of Information Technology of Peking University, Hangzhou, China

4:45 PM

# 3.9 A 0.5-to-400MHz Programmable BAW Oscillator with Fractional Output Divider Achieving 4ppm Frequency Stability over Temperature and <95fs Jitter

S. Mukherjee<sup>1</sup>, Y. Darwhekar<sup>1</sup>, J. Janardhanan<sup>1</sup>, P. Mirajkar<sup>1</sup>, R. Reddy<sup>1</sup>, H. Ramesh<sup>1</sup>, B. Bahr<sup>2</sup>, J. Chand<sup>1</sup>, U. Meda<sup>1</sup>, B. Haroun<sup>2</sup>, S. Karantha<sup>1</sup>, E. Yen<sup>3</sup>, K. Martin<sup>2</sup>, D. Gan<sup>4</sup>, A. Sijelmassi<sup>2</sup>, S. Aniruddhan<sup>5</sup>, <sup>1</sup>Texas Instruments, Bangalore, India; <sup>2</sup>Texas Instruments, Dallas, TX <sup>3</sup>Texas Instruments, Santa Clara, CA; <sup>4</sup>Texas Instruments, Melaka, Malaysia

<sup>5</sup>Indian Institute of Technology Madras, Chennai, India

# **Frequency Synthesizers**

Session Chair: Dmytro Cherniak, Infineon Technologies, Villach, Austria Session Co-Chair: Wanghua Wu, Samsung Semiconductor, Santa Clara, CA

1:30 PM

# 4.1 A 16GHz, 41kHz<sub>rms</sub> Frequency Error, Background-Calibrated, Duty-Cycled FMCW Charge-Pump PLL

P. T. Renukaswamy<sup>1,2</sup>, K. Vaesen<sup>1</sup>, N. Markulic<sup>1</sup>, V. Derudder<sup>1</sup>, D-W. Park<sup>1</sup>, P. Wambacq<sup>1,2</sup>, J. Craninckx<sup>1</sup> <sup>1</sup>imec, Heverlee, Belgium <sup>2</sup>Vrije Universiteit Brussel, Brussels, Belgium

#### 2:00 PM

## 4.2 A 135fs<sub>ms</sub>-Jitter 0.6-to-7.7GHz LO Generator Using a Single LC-VCO-Based Subsampling PLL and a Ring-Oscillator-Based Sub-Integer-N Frequency Multiplier Y. Jo\*, J. Kim\*, Y. Shin, C. Hwang, H. Park, J. Choi

Korea Advanced Institute of Science and Technology, Daejeon, Korea \*Equally Credited Authors (ECAs)

#### 2:30 PM

# 4.3 A 76.7fs-Integrated-Jitter and -71.9dBc In-Band Fractional-Spur Bang-Bang Digital PLL Based on an Inverse-Constant-Slope DTC and FCW Subtractive Dithering

*S. M. Dartizio*<sup>1</sup>, *F. Tesolin*<sup>1</sup>, *G. Castoro*<sup>1</sup>, *F. Buccoleri*<sup>1</sup>, *L. Lanzoni*<sup>1</sup>, *M. Rossoni*<sup>1</sup>, *D. Cherniak*<sup>2</sup>, *L. Bertulessi*<sup>1</sup>, *C. Samori*<sup>1</sup>, *A. L. Lacaita*<sup>1</sup>, *S. Levantino*<sup>1</sup> <sup>1</sup>Politecnico di Milano, Milano, Italy <sup>2</sup>Infineon Technologies, Villach, Austria

Break 3:00 PM

3:15 PM

# 4.4 A 32kHz-Reference 2.4GHz Fractional-N Nonuniform Oversampling PLL with Gain-Boosted PD and Loop-Gain Calibration

J. Qiu, W. Wang, Z. Sun, B. Liu, Y. Zhang, D. Xu, H. Huang, A. A. Fadila, Z. Liu, W. Madany, Y. Xiong, A. Shirane, K. Okada Takwa Jashirata di Tashaalami, Takwa Jasaa

Tokyo Institute of Technology, Tokyo, Japan

3:45 PM

# 4.5 A 9.25GHz Digital PLL with Fractional-Spur Cancellation Based on a Multi-DTC Topology

*G. Castoro\*1, S. M. Dartizio\*1, F. Tesolin1, F. Buccoleri1, M. Rossoni1, D. Cherniak2, L. Bertulessi1, C. Samor1*, *A. L. Lacaita1, S. Levantino1* <sup>1</sup>Politecnico di Milano, Milan, Italy <sup>2</sup>Infineon Technologies, Villach, Austria \*Equally Credited Authors (ECAs)

#### 4:15 PM

# 4.6 A 47fs<sub>rms</sub>-Jitter and 26.6mW 103.5GHz PLL with Power-Gating Injection-Locked Frequency-Multiplier-Based Phase Detector and Extended Loop Bandwidth

*J. Bang, J. Kim, S. Jung, S. Park, J. Choi* Korea Advanced Institute of Science and Technology, Daejeon, Korea

#### 4:45 PM

# 4.7 A 0.4V-V<sub>DD</sub> 2.25-to-2.75GHz ULV-SS-PLL Achieving 236.6fs<sub>rms</sub> Jitter, -253.8dB Jitter-Power FoM, and -76.1dBc Reference Spur

*Z. Zhang*<sup>1</sup>, *X. Shen*<sup>1</sup>, *Z. Zhang*<sup>1</sup>, *G. Li*<sup>1</sup>, *N. Qi*<sup>1</sup>, *J. Liu*<sup>1</sup>, *Y. Chen*<sup>2</sup>, *N. Wu*<sup>1</sup>, *L. Liu*<sup>1</sup> <sup>1</sup>Chinese Academy of Sciences, Beijing, China <sup>2</sup>University of Macau, Macau, China

# Image Sensors

Session Chair: Kazuko Nishimura, Panasonic Holdings, Moriguchi, Japan Session Co-Chair: Masaki Sakakibara, Sony Semiconductor Solutions, Atsugi-shi, Japan

#### 1:30 PM

# 5.1 A 3-Wafer-Stacked Hybrid 15MPixel CIS + 1MPixel EVS with 4.6GEvent/s Readout, In-Pixel TDC and On-Chip ISP and ESP Function

M. Guo<sup>1</sup>, S. Chen<sup>1</sup>, Z. Gao<sup>2</sup>, W. Yang<sup>1</sup>, P. Bartkovjak<sup>2</sup>, O. Qin<sup>2</sup>, X. Hu<sup>1</sup>, D. Zhou<sup>1</sup>, M. Uchiyama<sup>2</sup>, Y. Kudo<sup>3</sup>, S. Fukuoka<sup>3</sup>, C. Xu<sup>2</sup>, H. Ebihara<sup>2</sup>, A. Wang<sup>2</sup>, P. Jiang<sup>2</sup>, B. Jiang<sup>2</sup>, B. Mu<sup>2</sup>, H. Chen<sup>1</sup>, J. Yang<sup>2</sup>, T. Dai<sup>2</sup>, A. Suess<sup>2</sup>

<sup>1</sup>OmniVision Technologies, Shanghai, China; <sup>2</sup>OmniVision Technologies, Santa Clara, CA <sup>3</sup>OmniVision Technologies, Yokohama, Japan

#### 2:00 PM

#### 5.2 1.22μm 35.6Mpixel RGB Hybrid Event-Based Vision Sensor with 4.88μm-Pitch Event Pixels and up to 10K Event Frame Rate by Adaptive Control on Event Sparsity

K. Kodama<sup>1</sup>, Y. Sato<sup>1</sup>, Y. Yorikado<sup>1</sup>, R. Berner<sup>2</sup>, K. Mizoguchi<sup>1</sup>, T. Miyazaki<sup>1</sup>, M. Tsukamoto<sup>1</sup>, Y. Matoba<sup>1</sup>, H. Shinozaki<sup>1</sup>, A. Niwa<sup>1</sup>, T. Yamaguchi<sup>1</sup>, C. Brandli<sup>2</sup>, H. Wakabayashi<sup>1</sup>, Y. Oike<sup>1</sup> <sup>1</sup>Sony Semiconductor Solutions, Atsugi, Japan <sup>2</sup>Sony Advanced Visual Sensing, Schlieren, Switzerland

#### 2:30 PM

#### 5.3 A 2.97µm-Pitch Event-Based Vision Sensor with Shared Pixel Front-End Circuitry and Low-Noise Intensity Readout Mode

A. Niwa<sup>1</sup>, F. Mochizuki<sup>7</sup>, R. Berner<sup>2</sup>, T. Maruyama<sup>1</sup>, T. Terano<sup>1</sup>, K. Takamiya<sup>1</sup>, Y. Kimura<sup>1</sup>, K. Mizoguchi<sup>1</sup>, T. Miyazaki<sup>1</sup>, S. Kaizu<sup>1</sup>, H. Takahashi<sup>1</sup>, A. Suzuki<sup>1</sup>, C. Brandli<sup>2</sup>, H. Wakabayashi<sup>1</sup>, Y. Oike<sup>1</sup> <sup>1</sup>Sony Semiconductor Solutions, Kanagawa, Japan <sup>2</sup>Sony Advanced Visual Sensing, Zurich, Switzerland

Break 3:00 PM

#### 3:15 PM

## 5.4 A 0.64µm 4-Photodiode 1.28µm 50Mpixel CMOS Image Sensor with 0.98e- Temporal Noise and 20Ke- Full-Well Capacity Employing Quarter-Ring Source-Follower

H. Kim, Y. H. Kim, S. Moon, H. Kim, B. Yoo, J. Park, S. Kim, J-M. Koo, S. Seo, H. J. Shin, Y. Choi, J. Kim, K. Kim, J-H. Seo, S. Lim, T. Jung, H. Park, S. Jung, J. Ko, K. Lee, J. Ahn, J. Yim Samsung Electronics, Hwasung, Korea

3:30 PM

## 5.5 A 16.4kPixel 3.08-to-3.86THz Digital Real-Time CMOS Image Sensor with 73dB Dynamic Range

*M. Liu<sup>1</sup>, Z. Cai<sup>1</sup>, S. Zhou<sup>2</sup>, M-K. Law<sup>3</sup>, J. Liu<sup>1</sup>, J. Ma<sup>4</sup>, N. Wu<sup>1</sup>, L. Liu<sup>1</sup>* <sup>1</sup>Chinese Academy of Sciences, Beijing, China; <sup>2</sup>Tianjin University, Tianjin, China <sup>3</sup>University of Macau, Macau, China: <sup>4</sup>Zhejiang University, Hangzhou, China

#### 3:45 PM

# 5.6 A 400×200 600fps 117.7dB-DR SPAD X-Ray Detector with Seamless Global Shutter

## **DS1** and Time-Encoded Extrapolation Counter

*B. Park*<sup>1</sup>, *B. Ahn*<sup>1</sup>, *H-S. Choi*<sup>2</sup>, *J. Jeong*<sup>3</sup>, *K. Hwang*<sup>3</sup>, *T. Kim*<sup>3</sup>, *M-J. Lee*<sup>2</sup>, *Y. Chae*<sup>1</sup> <sup>1</sup>Yonsei University, Seoul, Korea; <sup>2</sup>Korea Institute of Science and Technology, Seoul, Korea <sup>3</sup>Rayence, Hwaseong, Korea

#### 4:15 PM

#### 5.7 55pW/pixel Peak Power Imager with Near-Sensor Novelty/Edge Detection and DC-DC Converter-Less MPPT for Purely Harvested Sensor Nodes

*K. A. Ahmed\*, H. Okuhara\*, M. Alioto,* National University of Singapore, Singapore, \*Equally Credited Authors (ECAs)

4:45 PM

## 5.8 Dual-Port CMOS Image Sensor with Regression-Based HDR Flux-to-Digital Conversion and 80ns Rapid-Update Pixel-Wise Exposure Coding

R. Gulve, R. Rangel, A. Barman, D. Nguyen, M. Wei, M. A. Sakr, X. Sun, D. B. Lindell, K. N. Kutulakos, R. Genov, University of Toronto, Toronto, Canada

# **Advanced Wireline Links and Techniques**

Session Chair: Friedel Gerfers, Technische Universität Berlin, Berlin, Germany Session Co-Chair: Takashi Takemoto, Hitachi, Sapporo, Japan

#### 1:30 PM

# 6.1 A 112Gb/s Serial Link Transceiver With 3-tap FFE and 18-tap DFE Receiver for up to 43dB Insertion Loss Channel in 7nm FinFET Technology